If you see this in the last updated topic, no, this is not an engineer application. This is an update to all typos here (September 30 2023).

Before starting to answer everything:

- This device wasn’t tested to draw cool animations or programs. I am bad at programming a CPU to run a very complex program in

URCLAssembly (this is an edit, I had no idea what was URCL back then). - World download: CPUSRGP (SISD) - CPU-Style Graphics Processor Minecraft Map (hope ORE doesn’t filter it to another dimension.com here)

Minecraft name: 75rx

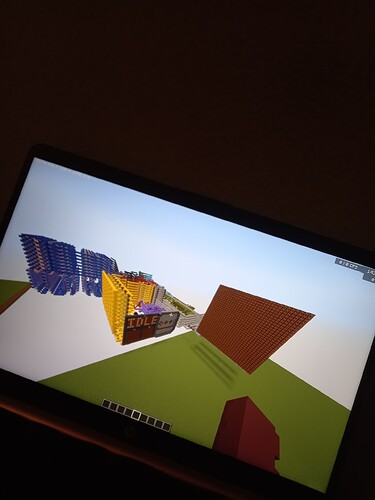

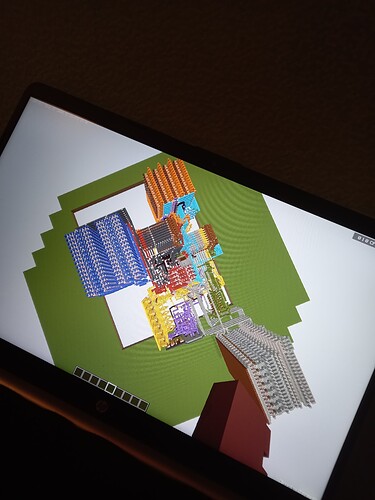

What’s a thing you have made which demonstrates sufficient engineering knowledge?: I’ve invented CPUSRGP (CPU-Style Redstone Graphics Processor). This is something most of players didn’t see.

This is basically SISD, but it is optimized to only render anything. For example, normally you plug X/Y coordinates with the help of I/O, but to create even more useful instructions relative to X/Y coordinates which are easier to do, even giving less headache when programming, I’ve made a special light gray device there. I call it Coordinates Device. Normally it obviously doesn’t exist, but it was decent to easily create awesome and useful instructions in this SISD. Now, you cannot use this as passthrough, unfortunately. But most of players don’t use it anyway.

Time to say specifications.

-

Overall

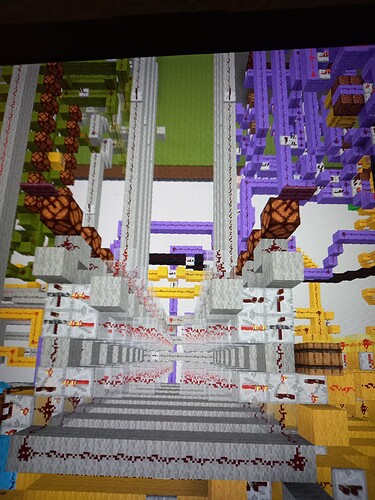

-Clock has multiple speeds which you can manage from the UI (User Interface). From 9 ticks which is obviously not recommended (1.11Hz) to 20 ticks for absolute snails (0.5Hz). Clock is purple btw.

-Program Counter is 6-bit, and default amount of program memory is 64 bytes. Thankfully you can destroy that type of program memory and add iCache with Hex RAM to increase the amount of program memory, or you can move the entire SISD up by a bit and add extra 2 bits to the program counter on the bottom, it will still work. Exactly, this SISD supports 8-bit of PC while it has 6 bits by default. The reason why you have to move is because it’s extremely close to the void - -62 blocks minimum Y height.

-3 operand RISC architecture with 5-bit opcode, 37 instructions with 8 NOPs, allowing you to add 8 of any instructions you like. This SISD is using MSC instructions (Miscellaneous), which is dark green part. This is to increase the amount of instructions. Obviously the ones that require MSC don’t require any operand.

-I guess 8-bit instruction length, I am assuming. -

RAM (Blue)

64 bytes worth of data RAM, not shared.

Addressed with registers

Serial RAM, probably the same one from the well-known sammyuri’s CHUNGUS2. -

ALU (Gray)

3 tick adder

Has basic control lines: FC, CIN, !A, !B, LSH, RSH, OR and Output Flood.

Accumulator and ALU is 1 same device, with the same color coding. -

Registers (Red)

8 bytes of DRR (because of 3 operand)

Addressed with the help of operand.

Very small yet fast. -

Control Unit (Brown)

Total amount of CUs: 3. They’re split: one is main, which interacts with ALU, Accumulator and Registers, second one interacts with coordinates and screen, and third one is being called by MSC instruction - so only instructions that can be used with the help of MSC + Operand.

Has very useful instructions and some my custom ones. With regards “useful”: RPC (Hope it exists, it’s Reset Program Counter), HLT, Pointers, and a lot more. There are 37 instructions and 8 NOPs as explained earlier. -

Flags (Black)

3 Flags: C, !C and 0. This is because I saw these are the most popular flags in 2022 in Minecraft CPUs.

Flags get ANDed by your operand. I think 100 is 0, 010 is C and 001 is !C. They also get ANDed by the PRD instruction - so there’s triple AND going on. The output of flags will cancel whatever is sending to the CPU, and will also show that one X in the UI. -

PMEM / PC (Orange)

Includes JID/JMP (Pointers) and RPC. As explained earlier.

6-bit PC and 64 bytes of PMEM. I have already said most of the stuff relative to this.

Although this SISD isn’t pipelined, immediates obviously are. -

Coordinates Device / Display (Light Gray)

16x16 display. This GPU supports up to 256x256, which is insane.

Can do: New frame, Reset Display and Draw pixel internally - all with the help of program memory - yes, you can code it that easily - there’s actually the instruction to interact with the screen.

You can get the coordinates and hook it up into your screen directly here:

It even tells you which axis is which.

What engineering work went into designing this device?: September 2021 - the month/year of me joining on ORE for the first time. I was slowly becoming better at redstone, but then I saw KilledbytheTV say something like “yeah fibonacci sequence loads like 30% of the CPU”. I teleported to him to see what he made, and oh my gosh, I wish I could run programs myself.

I kept asking for help from players about computer and CPU components. I was learning slowly, but everything was getting better and better.

Oh no! I got banned! I gotta wait for 6 months now.

…

Okay, finally unbanned.

And then I kept learning even more components and instructions of the CPU - even faster.

Until I made ExecutableMinec- oh. Exactly, that CPU was very buggy. And instruction pipeline(!) was the reason +RAM. Fixing it could take a ton of time.

So, I asked Koyarno about “can I still get an Engineer if I make a good enough CPU-Style GPU that’s not pipelined?”.

He said something similar to yes. Got happy and built this. This CPU is far more stable because it isn’t pipelined. There might be bugs still - I was fixing bugs and modifying world downloads for my EMC2 exactly 10 times(!). This is hilarious, since it still doesn’t work. But this CPU is a lot better.

This is why you should NEVER give up. It’s been exactly a year now and I made this.

What’s even more respectful is I am actually 10 years old (11 tomorrow) and I make stuff like this. Never seen anyone else that’s 10/11 years old make this. I am probably the first one ever.

Image/s and/or video/s of the device:

I’ll upload YT Video soon.

Lol, I cannot take a picture. It says Unable to do this operation because of low memory and then just saves this as a draft. I tried multiple times.

If you still need some images, let me know.

-75rx, September 28 2022.