Hi all, I’m a CS student who’s recently gained interest in logical redstone as it allows me to learn in a more interactive way about digital systems.

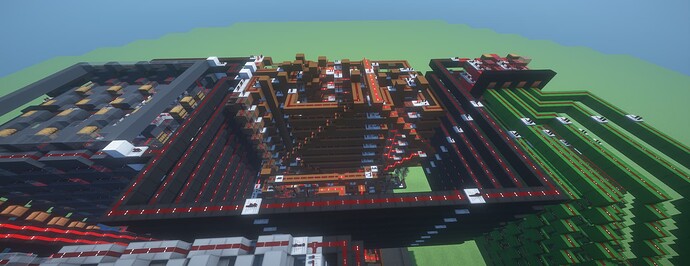

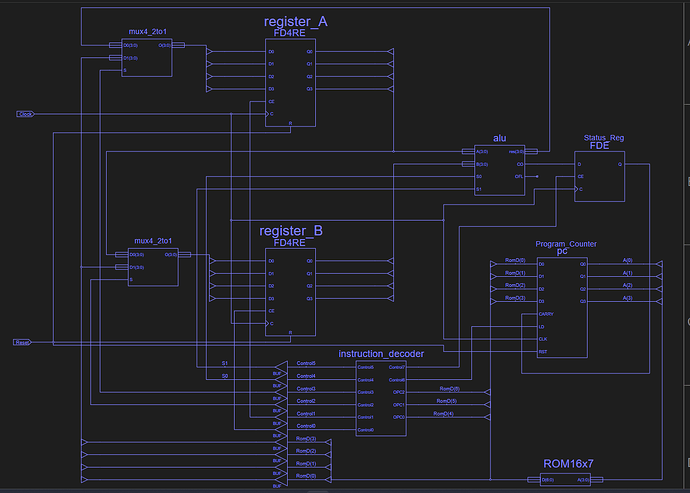

I’ve been watching some of mattbatwings’ videos and recreated a very slightly altered version of his CPU. I rebuilt the ALU from his cancel-carry adder tutorial and slapped some additional controllable gates on top such that I can reproduce all the operations but in a slightly different way. For example, AND is produced by XOR’ing the final output with the OR signal among other differences. Probably less efficient, absolutely less compact for sure, but slightly easier for me to wrap my head around than the one built with sammyuri (the layers overlapping and mixing to make it more compact makes it quite difficult to figure out what’s going on).

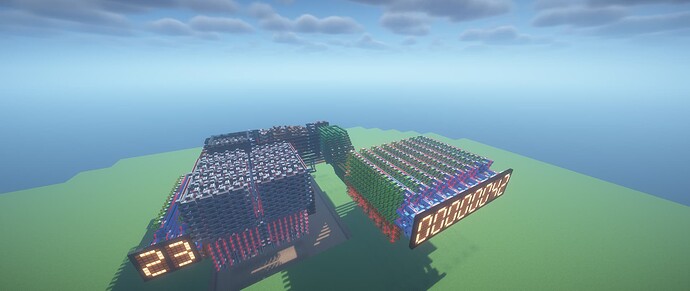

I copied the ROM, register file and HEX segment displays outright from his world downloads and connected them to my own ALU. Being able to use a modified version of the assembler script from matt’s Github is a bonus because writing the ROM by hand is a pain. I do intend on writing my own in Rust because that seems like a fun way to finally start learning Rust.

I have added ADC and SBC (pseudo) instructions which take in the contents of the carry registers such that you can work with numbers larger than 8-bits. I freed up an opcode by only having a branch instruction with 3 bits as argument that encodes the branch condition (111 being ‘always’, 000 ‘carry,’ 001 ‘not carry’, 010, ‘zero’ and I have some left over for things like equal, greater than by combining the status registers). The ‘jmp’ instruction is just a pseudo instruction that resolves to “bif always” so I don’t need that opcode. There’s no RAM yet, altough I can use the registers for the HEX display as memory mapped IO.

Building this helped me better understand how the clock signal must affect each component such that there is no state change when storing new data in the registers. Writing assembly and seeing it work like this is also really fun and new for me. The program here is performing the double-dabble algorithm (the display on the right just displays the contents of 4 registers in HEX without hardware BCD conversion, the display on the left is the current memory address).

Anyway, on to my question. I’m interested to know to what extend these design’s are all from Matt himself or whether the various design ideas are just iterations of other people’s work. Is it common practice / accepted to re-use designs? I wouldn’t call this thing I’ve put together for my own education “my own” as it’s almost a literal copy of the one by mattbatwings, but to what extend can you re-use components?

I’m mostly interested in learning the logic and design principles that translate to the real world, not so much in finding Minecraft specific ways to make the most compact redstone designs ![]()

Now I’m just really interested in how a pipelined CPU would work, how caching works, branch predictors and what have you. The program counter is now a separate component that can be written to with an instruction but a “real” CPU keeps it in a register such that you can keep a stack in RAM for subroutines/functions, but then how is it incremented? with the ALU? So many things to explore.

P.S I just made up the username just now, I don’t use it anywhere else. It means redstone in Afrikaans in case you were wondering (No I’m not South-African, I just found it a funny word)