Minecraft name: pishleback

What’s a thing you have made which demonstrates sufficient engineering knowledge?:

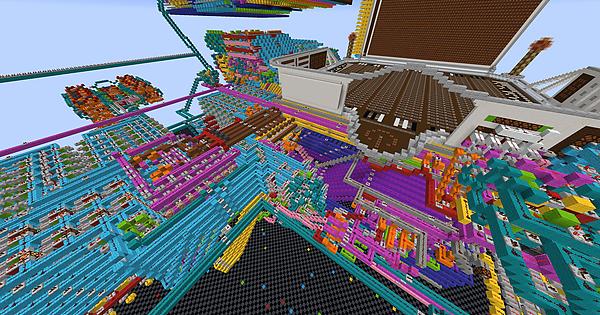

An 8 bit CPU designed to run general purpose programs with a focus on ease of use.

Overview of specs:

- 256 nibbles of program memory

- 8 bit

- 16 registers

- 27 bytes of data stack

- 16 bytes of call stack

- 6 tick clock per nibble of program (excluding jumps and IO)

- ALU instructions include and, or, xor, add, not, bitshifts

- 14 (non-trivial) branch conditions

- error detection (stack overflows, and IO error when going too fast for the protocol)

- unlimited number of IO devices with serial protocol

What engineering work went into designing this device?:

This CPU is something I have wanted to build for almost a decade. Learning how a computer works and building my first CPU was the first step and I learnt how to build RAM, registers, and an ALU. Since then I have made over 10 others, each making slight improvements over the previous one and trying new things. I list some of the key steps here:

-

using CCA adders and switching to vertical buses: this allowed for much smaller, faster, and more precisely timings in my CPUs.

-

tick-perfect timing and pipelining: By making sure every redstone wire was timed down to the tick, I got big speed improvements as well as reliability.

-

deciding that usability is more important than compactness and speed alone: I realised that I was making fast CPUs which I didn’t enjoy using once they were complete - this changed my approach so that usability became the top priority above both speed and compactness.

-

“unlimited” IO addresses and IO protocol: I often found that I either didn’t have enough IO addresses, or that there were far too many. This led to annoyance and/or clutter. To fix this I switched to using a single pair of wires which connected to every IO device along with an IO protocol: I won’t explain exactly how it works here but the result is a system with no wire clutter and no limit on the number of IO devices. The downside is a loss in speed however as stated earlier I was more concerned with usability and the ability to add and remove IO devices without worrying about wiring or address space came before speed.

The CPU I present for this application is the culmination of all these factors and almost 10 years of experience.

Image/s and/or video/s of the device: