Minecraft name:

tyiy123

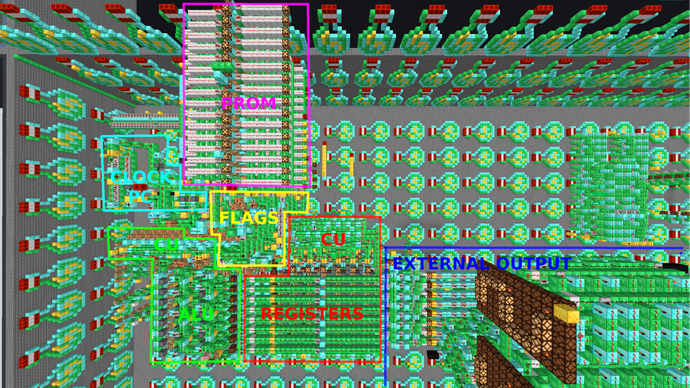

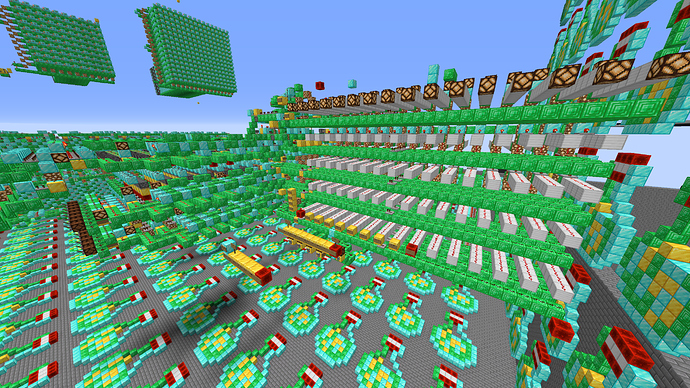

What’s a thing you have made which demonstrates sufficient engineering knowledge? : 8bit CPU at 0.714Hz, implementing :

=16 instructions stored in PROM

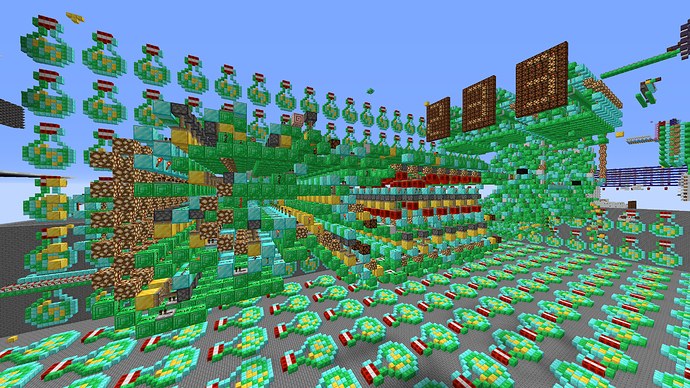

=Complete 8bit ALU (6ticks) with all the logic gates in addition to two arithmetic operations and shifts, and 3 slots available for “needed functions” to be implemented later. They are all 3 operands, and includes:

- ADD

- SUB(A-B)

- OR

- AND

- INC *((A + B) +1)

- RST *((A + B) >> 1)

- XOR

- LST *((A + B) << 1)

- DEC *((A + B) - 1)

- NOR

- XNOR *(NOT A)

- NAND

- SUB(B-A)

- ???

- ???

- ???

=The ALU supports to set 5 flags into a flag register :

- Underflow flag

- Overflow flag

- Carry OUT

- Sign Bit

- Zero flag

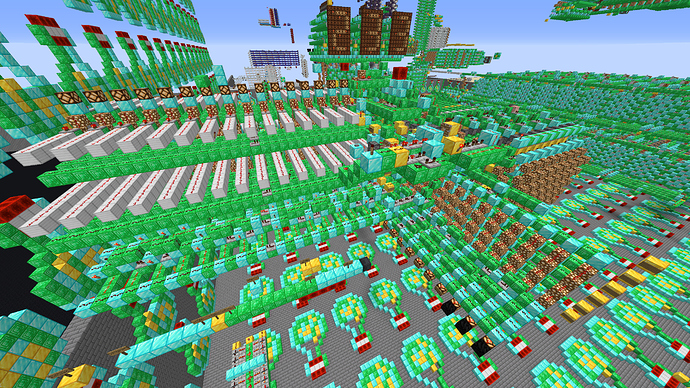

=7 8bit dual read registers (5ticks) and an 8bit external IO (A, B, OUT)

=Unconditional branching

=Conditional branching using flags or number comparisons after CMP instruction (all implemented) :

- JU (UF)

- JO (OF)

- JC (COUT)

- JS (SB)

- JZ (ZF)

- JE (A == B)

- JG (A > B)

- JGE (A >= B)

- JL (A < B)

- JLE (A <= B)

- and all these possibly negated.

Every instruction may be performed by reading any registers (or external input), writing to any register (or external output) and writing all 5 flags. Registers are available directly for the next instruction (even for branching).

What engineering work went into designing this thing? :

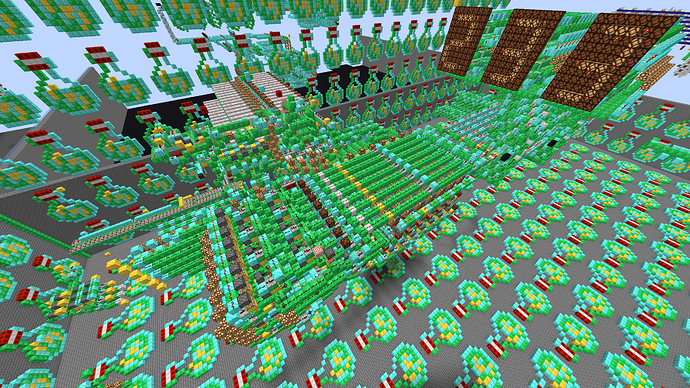

At the beginning of the project, I wanted to create a Turing complete CPU all by myself in Minecraft. Thus, I made everything in this CPU, from the XNOR gates (maybe it resembles to someone else’s at this basic level), the binary full adder, the features of the ALU, the ALU itself, its CU for 16 functions, the registers, its CU for 7 of them in addition to external IO, all the buses, the 16 instructions PROM, the instruction decoder, the program counter (though inspired by someone else), the 9/5 clock, the branching on the PC, the flags register, reader and inverter, etc. Everything in fact.

Moreover, I really wanted to get the clock as fast as possible by synchronizing everything down to its minimum (6ticks ALU is superb). I had difficulty for writing to registers first, because it would not write on the rising edge of a pulse, only at the falling. Much work had gone in this for the data to be available directly at the next instruction.

On another hand, I wanted to support as much functions and conditions as possible within one instruction (and one cycle). That’s why all logic gates, most flags and all conditions are there, including negating them all.

I wrote two programs for it right now, however a lot more to come : Fibonacci and multiplication, linked with a 7 segments display made by myself (although the idea came from someone else).

Image(s) and/or video(s) of the device :