Minecraft name:

_rtyyyyb

What’s a thing you have made which demonstrates sufficient engineering knowledge?:

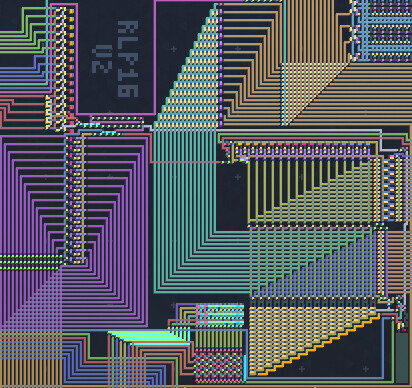

i made my RLP16 V1 and V2 cpus

RLP16 V1 specs:

- 32 tick clock

- 32 general purpose registers

- 131kb of ram

- 64k max program size (in terms of lines)

- 16 bit word size

- 32 bit instruction word( 16bit imm, 4bit opcode, 5 bit register address, 3 bit io address, 4 bit condition)

- 13 jump conditions

- 8 IO ports

- (plus other less general specs)

RLP16 V2 specs:

- 32 tick clock

- 32 general purpose registers

- 131kb of ram

- 64k max program size (in terms of lines)

- 16 bit word size

- 32 bit instruction word(16bit imm, 5bit opcode, 5 bit register address, 6 bit changeable)

- 14 jump conditions

- 32 deep hardware FILO call stack

- 128 deep hardware FILO data stack

- 4 IO ports (up to 64)

- 64x48 3 bit rgb screen

- custom keyboard

What engineering work went into designing this device?:

the main goal of both V1 and V2 was to be able to run really fast but also be very capable which required a smart balancing of complexity and total gate count.

after making my RLP32 cpu i realized that the word size doesnt affect the performance of the cpu in many ways and that its better to make a more complicated cpu rather than a big on that barely works (why i stooped making titan computer) and for these 2 cpu i focus more heavily on making the cpus more complex and have more functionality.

RLP16 V1:

RLP16 v1 used a 32 bit instruction word comprised of: 16bit immediate value, 4bit opcode, 5 bit register address, 3 bit io port address and 4 bit condition type. since i wanted the cpu to be as fast as possible i didnt want to waste cpu cycles simply loading in a immediate so i allocated the bottom 16 bit to be the immediate value and that would always output to the bus that way i could use a imm value for any of the instructions which greatly reduces the program size. for the conditions the ALU outputted 6 flags: carry out, greater than, less than, equal, right shift carry and left shift carry which i could then put in to a sort of gate array which i could use to make 13 separate conditions which i directly fed in a 16 to 1 MUX which was controlled by the condition type. the muxes output was then hooped up to a AND gate with the JMP control line as the second input. the output would then go into a switcher which depending on the and gate being TRUE or FALSE would decide whether to jump next cycle of step next cycle.

RLP16 V2

now the RLP16 Y2 was a major improvement to V1 as the original even tho it had complete imm support it was still quite limiting in some cases. the biggest improvements where the extended alu and the 32 deep hardware call stack (data stack as well) this cpu also had twice as big of a ISA compared to V1 as it made full uses of the alu capability and also adding other more complex instructions like CAL and RET which was the first and hardest instructions to implement as it required a lot of extra hardware that couldn’t be re used form V1. it also cam with a lot of debugging as it often had data errors or false jumps due to the fact it would have to psh pc + 1 to the stack and then jump to a different address all in one clock cycle and it had to be tick perfect of it wouldn’t work. in the V1 i didnt make use of the alus full capability as i was limiting myself to 16 total instructions where as in V2 i made full use of it and most of the isa was alu instructions. they include: ADD, SUB, MULTL MULTH, AND, OR, XOR, NAND, NOR , NXOR, RSH, LSH. BRSH AND BLSH. for the conditions i also added one extra which which was mult overflow which was simply if a multiplication resulted in a value bigger than 16 bits.

NOTES:

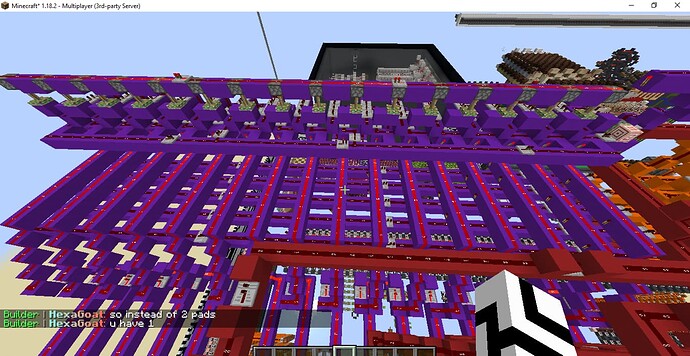

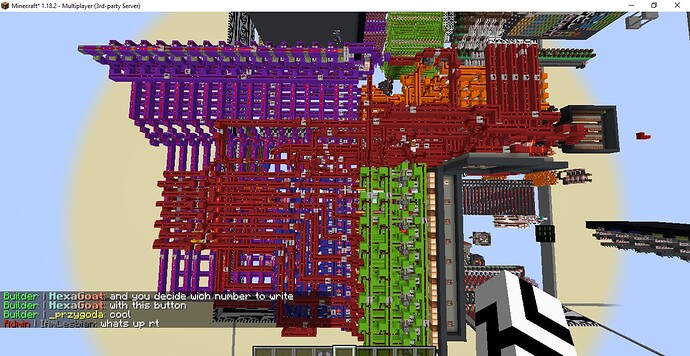

both these cpus were made an ram in VCB. BUT no where in the rule on applications does it have to be redstone specifically and also they both still show off my knowledge and capability as well… they work (also the could be built in mc which little problems)

PROGRAMS:

V1:

- fibonachi (auto stop)

- 64 bit fibonachi

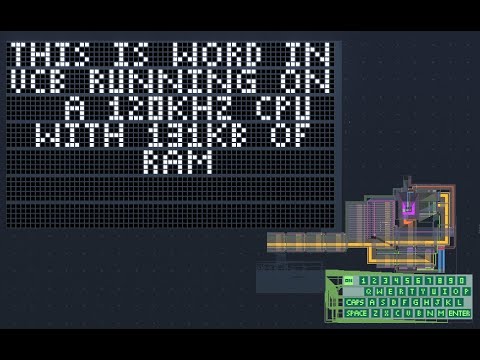

- word processor

- pong

- move a cube program

- semi functional function system (aka bad CAL and RET

V2: - fibonachi (auto stop)

- line drawer

- fibonachi (displayed)

- rgb screen test

( i only recently made V2 so i haven’t coded much for it

Image/s and/or video/s of the device:

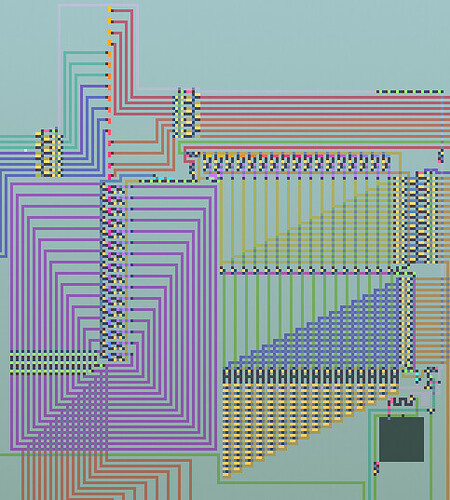

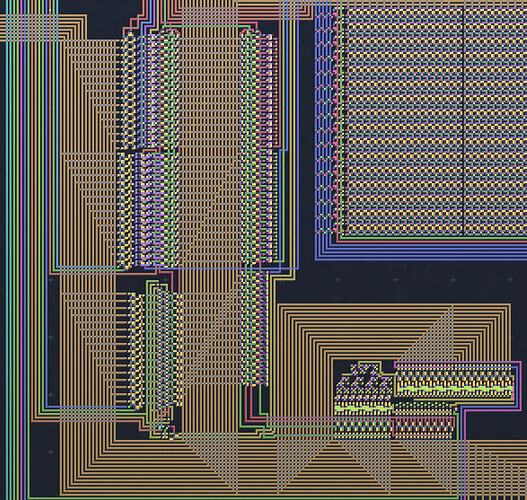

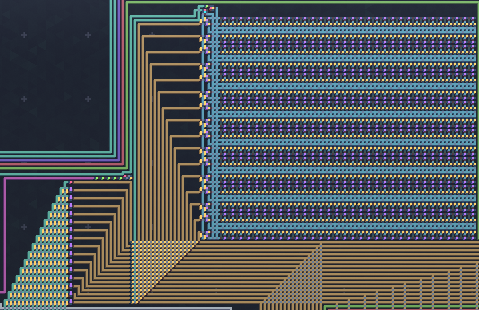

RLP16 V1:

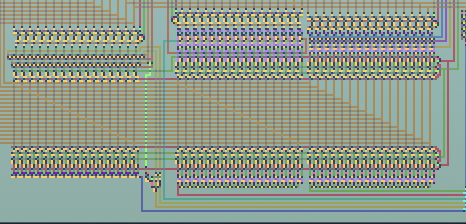

ALU:

REG FILE:

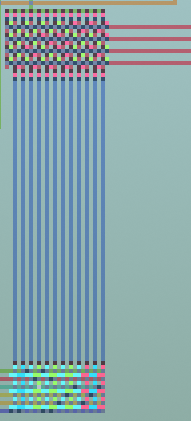

control unit:

ram and program interface:

conditions circuit:

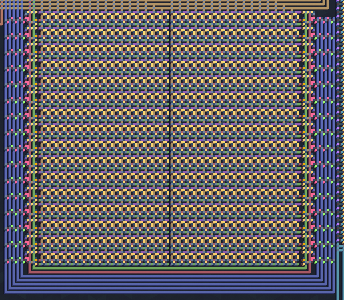

entire cpu:

programs:

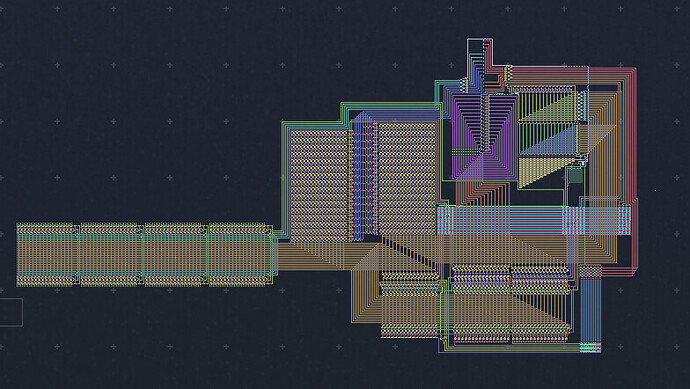

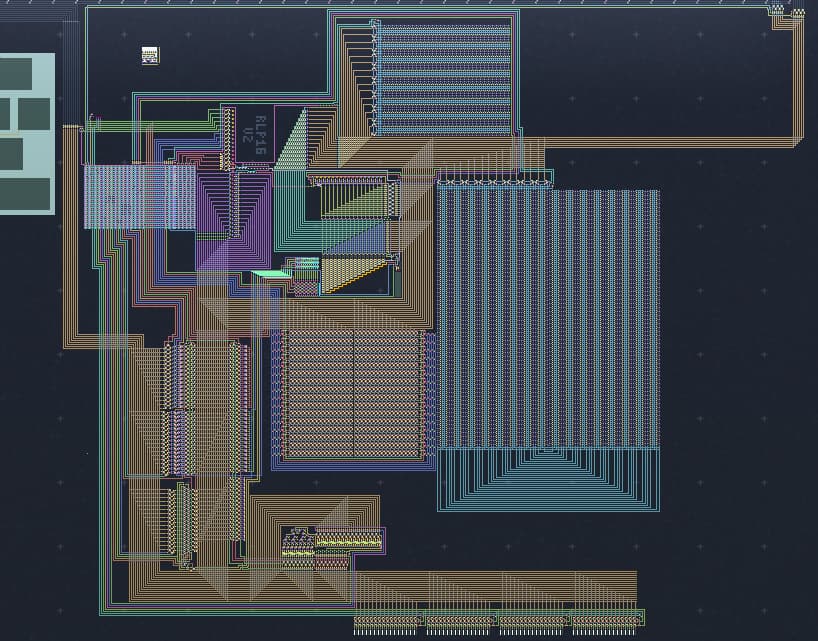

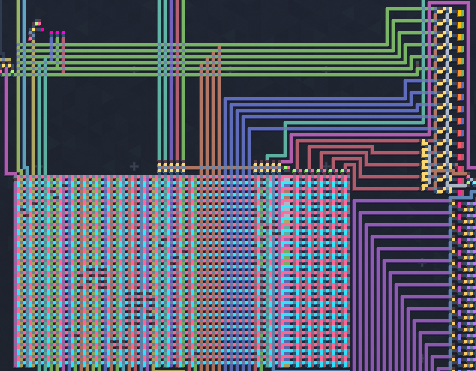

RLP16 V2:

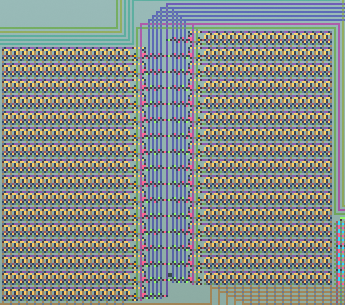

ALU:

REG FILE:

CALL STACK:

control unit:

program and ram interface:

entire cpu:

PROGRAMS:

(i currently have not vid of the cpus program on yt but i would be happy to show you in a vc or such)

PS: i just like to re iterate that the cpus aren’t in mc doesn’t mean i dont have both the knowledge of cpus and the skills to make them. so please take this in mind when judging