Minecraft name:

skullXbagel

What do you like the most about redstone?:

It’s simple(ish) but complex enough to do anything you need with it.

What’s a thing you have made which demonstrates redstone knowledge?:

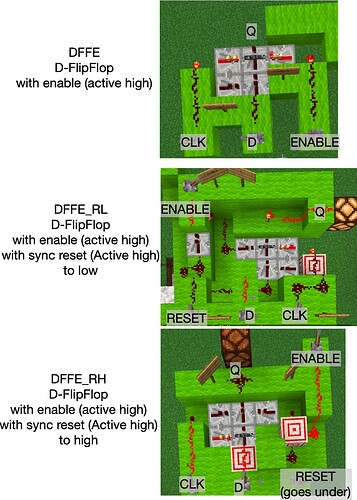

I made a set of three sequential logic gates:

- DFFE: D-Flip Flop with Enable

- DFFE_RH: D-Flip Flop with Enable and Synchronous reset to high

- DFFE_RL: D-Flip Flop with Enable and Synchronous reset to low

This is part of an ongoing project which will eventually require worldedit to test where I am using industry-standard synthesis and place-and-route tools to compile circuits for minecraft. To interface well with these tools, all cells that I can use must

- have the same height (I’m choosing 4 because I haven’t been limited by height 4 yet), but can use arbitrary depth and width.

- the input pins must be diodes: driving one pin cannot drive an unrelated output pin

- sequential cells should ideally have symmetric timing arcs: arc from D to Q ~ EN to Q

I would show some of the pictures of the result I have right now with the tools but I can only post one image at a time…

What does the thing do?:

- DFFE : when the enable signal is high then on the positive edge of the clock, it latches the D pin (input) to the output (Q). If enable is low, the output never changes

- DFFE_RL: Same as DFFE, but when the reset signal is driven then, regardless of the enable pin, it resets the output (Q) to low on the posedge of the clock

- DFFE_RH: Same as DFFE, but when the reset signal is driven then, regardless of the enable pin, it resets the output (Q) to high on the posedge of the clock

Even though the RL and RH flavors are similar, the RL cell ended up being much more complicated.

Image(s) and/or video(s) of the device:

I know that everyone else likes vertical and diagonal gates but they just don’t play well with the tools I’m using so I’ll think about using them later and, in the meantime, I only really care about horizontal gates.

What did you make as your trial build?:

The above cells.

What is the warp for your trial build?:

bagelTrial

Provide your results after completing the ORE Binary Quiz:

Binary Quiz completion certificate:

Completed by skullXbagel in 3m0.983s on 11/29/2024, 16:56 UTC.

100.00% accuracy with 0/25 answers given incorrectly.

546d4a72-fda9-4be1-855e-5283a86cb7cd-736b756c6c58626167656c

3t2u24241g5x606l673q1z6a336e3i2z2k6y3w5wm42zg872m42zk3ud

Do you agree with the rules?:

Yes.