Minecraft name: _Torb

What’s a thing you have made which demonstrates sufficient engineering knowledge?:

I have made the Helium CPU a pipelined 10t processor that is accumulator based. I made it to run advanced and long programs by having 512 Bytes of Program ROM and 16 I/O ports. The point of having that many I/O ports, is to be able to easily expand the cpu with dedicated hardware, so it can run more complex programs at a decent speed.

General Overview:

-8 bit

-8 general purpose Registers

-10t clock

-512 Byte of total Program Rom (16 pages)

-32 Byte Icache

-32 Byte ram (with Pointer expandable to 256 Byte)

-9 ALU instructions

-16 I/O ports

-4 flags which can be combined

Helium has the “classical” 3 Stage Fetch, Decode, Execute pipeline. I went with this shorter and simpler pipeline because, while it might slow the clock down a bit, you do not have to deal with data hazards and you only get one flag delay slot, which in return kinda compensates for the slower clock.

One of the register doubles as a pointer for ram. Speaking of ram the 32 Byte might seem a bit limiting, but due to the ram being able to be read from and written to without stalling nor any hazards, it makes it quite nice. Obviously you could expand the ram to up to 256 Bytes by using the pointer or hooking up some external ram to one of the I/O ports.

The cpu has 4 flags which can be ORed together to make some more complex conditions. The flags are: CarryOut, Negative(MSB), 0 Flag and Odd/Even(LSB). Rather than branching Helium uses predication.

Immediates are handled trough a 2 Byte instruction.

I also wrote a assembler in python, which converts written assembly to schematics, to be easily able to run and debug larger programs without having to manually manipulate the rom.

https://drive.google.com/file/d/1bIDV3Zk_3NFN3yBti9mEU3XAxdwBFnDz/view?usp=sharing

Some more stuff like ALU instrctions can be found in the ISA:

Also im currently working in a logisim “emulator” and a simd coprocessor.

What engineering work went into designing this device?:

Redstone has always interested me and when i finsished my first redstone computer i was hooked into computational redstone. What followed was my buggy and weirdly pipelined 1Hz cpu. After joining ORE and getting Builder i wanted to improve upon that, so i started making Helium.

The main things i wanted to improve on were a better ISA, program rom size, ease of use, I/O and reliability (also a better shape and no bistons).

The ISA was inspired by several existing ISAs including the predication from BBV2. But this was just the first iteration of the ISA which was changed several time throughout the building and debugging process to fit my needs better.

First i made the layout of the cpu, by fitting all the different parts together in a square. Then i added the control unit in the remaining space. What i was left with was the first kinda buggy prototype. After realising i missed a right shift(bruh) i added it by adding another instruction. Then realising i missed pointer support and i had no place for instruction decoders anymore, i mapped memory address 0 to the pointer. This allowed me to run some nice programs like sorting and pong. But they were quite slow so i decided i wanted to have it be MCHPRS compatible. This lead to me redesigning the program rom (which previously used observers) and icache to be compatible. Altough the page load are quite a bit slower with MCHPRS in total the whole cpu runs faster, which lead to me being able to render the mandelbrot set on it. I think the result of going back and forth has reached a point were i like it.

Image/s and/or video/s of the device:

Helium running bubblesort on an array of 16 numbers

Successfully rendered 64x65 Mandelbrot

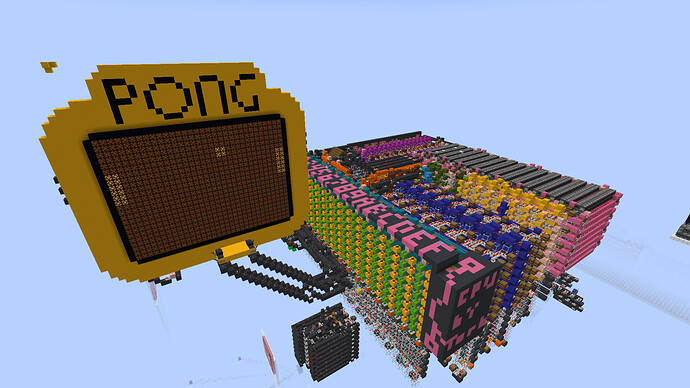

2 Player Pong

Front view with Interface

I also made some more “basic” programs like fibonacci, multiplication, squareroot and the such.